Advanced Design Verification

Explore Verification concepts through hands-on projects and expert guidance in UVM verification.

Eligibility

Overview

The Advance Digital Design course is structured to provide practical experience in designing and creating a smarter testbench of complex design and bus protocols.

B.Tech/Diploma in EEE, ECE & EIE pursuing or completed.

M.E/M.Tech/M.S in VLSI/Embedded/Any other specialization.

Working Professionals.

Any one curious!

Mode of Study

Online Mode.

Offline Mode (Kolkata, West Bengal).

Learning Outcomes

Mastering the art of designing the circuit on a piece of paper and verifying it with UVM.

Key Course Features

Demo class Available.

Job assistance and tool support.

Industry live projects under the supervision of 12+ experienced trainer.

Course material, hand-outs, quizzes, assignments to assist in learning.

Course Features

Duration - 4 to 6 Months

Skill Level - Advance

Language - English

Assessments - Yes

Job assistance - Available

Curriculum

Advance Digital Design using Verilog.

System Verilog for Verification.

UVM Methodology.

Projects.

Bash Scripting.

Advance Digital Design using Verilog

Introduction to the course.

Basic Digital Electronics.

Advance Digital Design on Paper.

Introduction to HDL (Verilog).

Project HMS counter.

Functions/Tasks, Operators, Race conditions.

Verilog event regions, Stratified event queue.

Projects 2 - FSM based UP-Down counter, Mod 4 Mod 5 counter, FIFO design (Unique approach!).

System Verilog for Verification

Introduction to the Course, Why System Verilog?

SV data types, Interface, Program block.

SV event region, TB and RTL race condition, self-checking TB.

OOPs, Class, inheritance, Polymorphism.

Randomization, Constraints, Inter process communication.

Implementing self-checking TB in pure verilog for D flip-flop.

What is static class ? How to implement Singleton object.

Code/Functional Coverage.

UVM Methodology

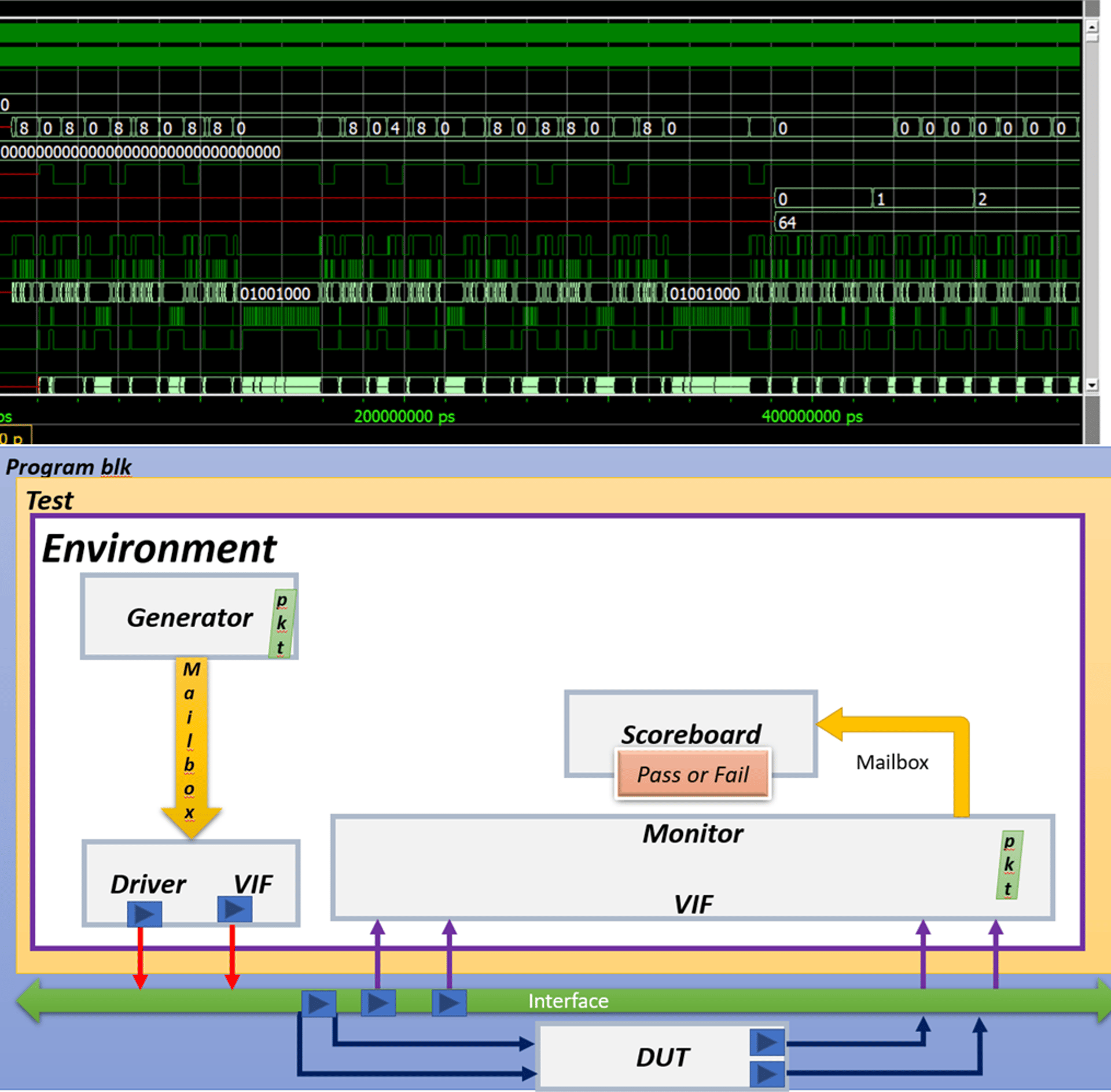

Introduction to the Course, UVM environment, UVM Messaging.

UVM transaction.

UVM Phasing.

UVM sequence, UVM configuration, uvm_config_db.

UVM TLM port, UVM Scoreboard, uvm_inorder_class_comparator.

UVM Testbench (Phase, Driver, Monitor, Agent, Scoreboard, Environment, Comparator, Test).

UVM DPI.

Projects

Verification Environment of CSR (Control and Status register) based memory model.

Creating a self-checking testbench in UVM for APB based slave memory.

Introduction to AXI Lite bus protocol.

Scripting

Shell commands. Grep, AWK, SED, FIND, Pipe (|) usages.

Introduction to Bash.

Using Makefile to automate/streamline the compile, elaboration and simulation stage.

Automated repot generation.

Creating a TB infra and understand how regression works.

Above units will be updated based on the latest industry related projects and interview questions.

Contact +91 9435136663 for offers!

Course Fee

Innovate

Join us to transform your VLSI career today.

Contact

Follow

+91 9435136663

© 2025. All rights reserved.